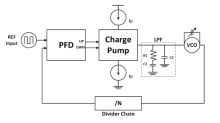

Phase locked loops are a critical component in modern communication, sensing, and imaging systems. While computer automated design tools allow for accurate simulation, they often take weeks of design and computing time. Our project's research intends to model a specific non-ideal performance of analog phase locked loops, previously not studied, as closed form equations. This allows designers to observe their system's performance in seconds, rather than weeks.

Equations for the varactor non linear behavior are derived and plotted in MATLAB. A 10 GHz analog phase locked loop schematic is created and simulated in Cadence Virtuoso using GlobalFoundries 22nm PDK. Cadence simulation outputs are transferred to MATLAB for direct comparison between simulation and mathematical models to demonstrate improvements in speed-to-accuracy metrics. Finally, design suggestiosn are given based on new equations generated to mitigate unwanted behavior.

Final equations are found for phase locked loop output and control voltages, modelling the target behavior. The equations only consist of design and manufacturing parameters that are known prior to simulation. Simulation and mathematical models are compared in MATLAB, and further work is needed to match simulation and mathematical measurements. A paper is currently being created to summarize research results and conclusions.